Lab1, Lab2

•

간단한 베릴로그와 DFA 문제

Lab3

•

Single-cycle CPU를 구현해보자

•

구현해야하는 명령어

LUI, AUIPC → U type

JAL → J type

JALR → I type

BEQ, BNE, BLT, BGE, BLTU, BGEU → B type

LG, LH, LW, LBU, LHU → I type Load

SB, SH, SW → S type

ADDI (arithmetic), SLTI, SLTIU (conditional), XORI, ORI, ANDI(logical), SLLI, SRLI, SRAI (shift)

ADD, SUB{signed,unsigned}, SLL, SRL, SRA, (Shift) SLT, SLTU,(Conditional) XOR, OR, AND(Logical) - Rtype

•

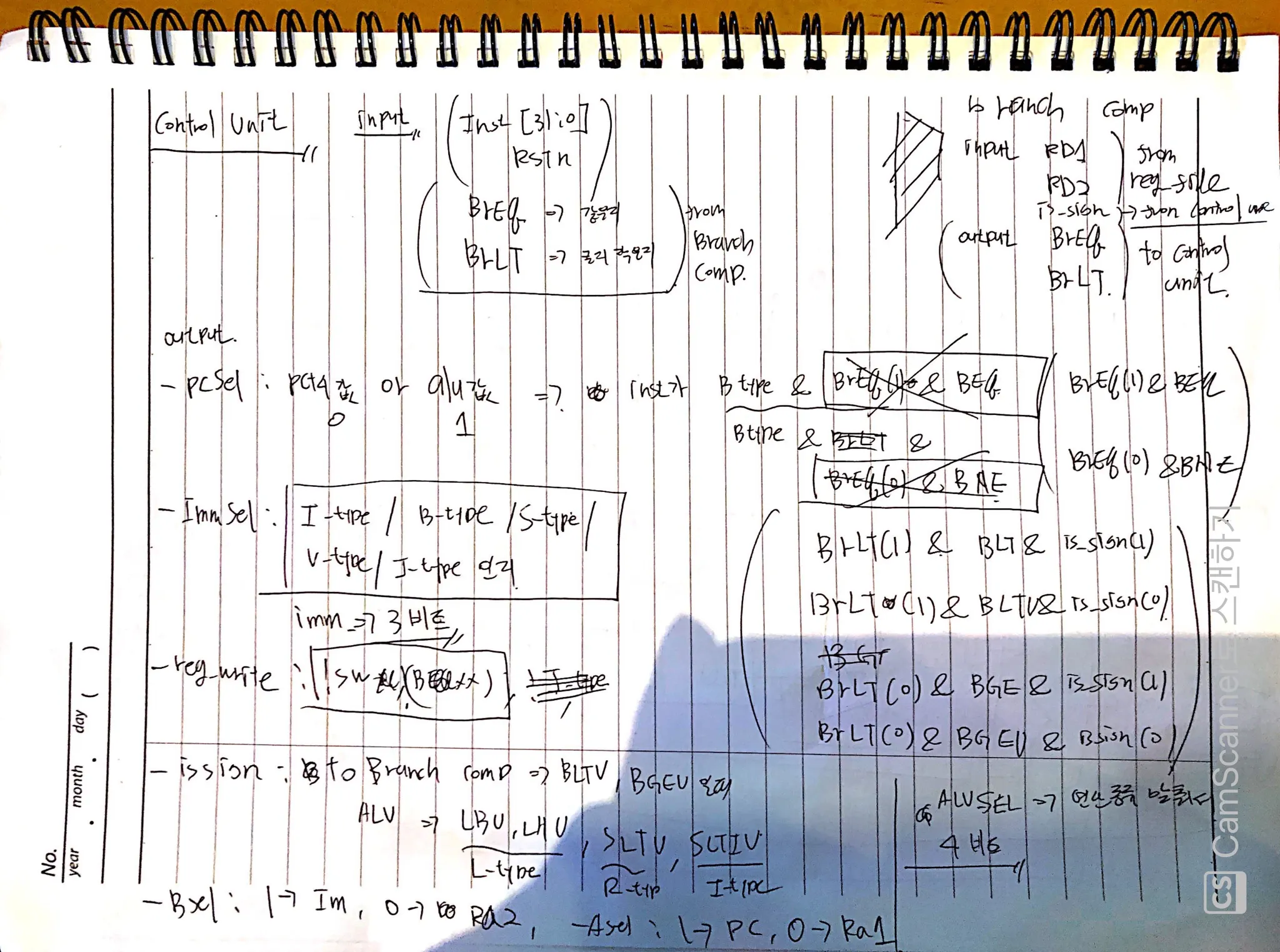

Design

Lab4

•

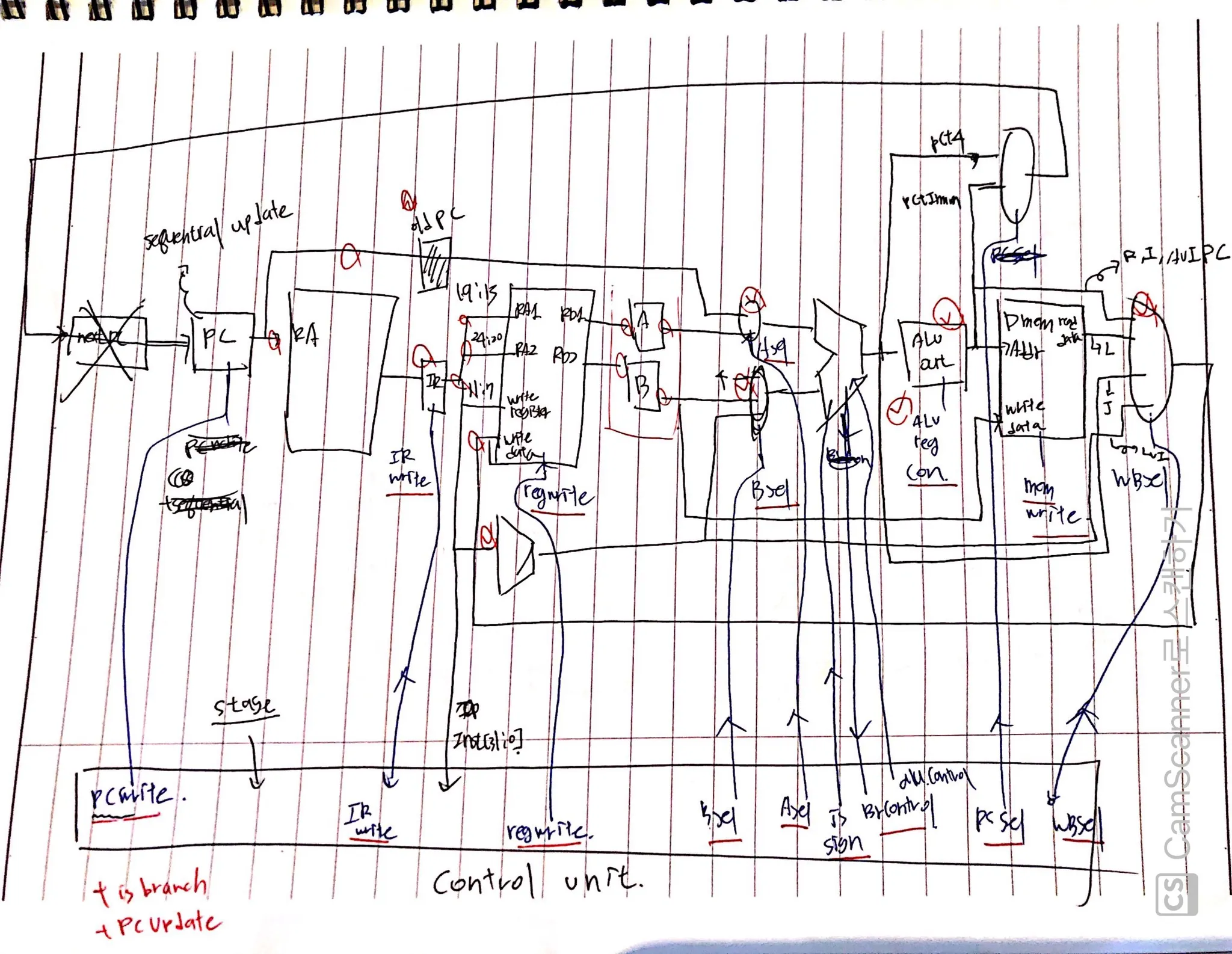

Multi-cycle CPU를 구현해보자

•

명령어에 따라 다섯 개의 State(IF-ID-EX-MEM-WB) 중 어떤 것을 거치는지 확인

•

Control Unit은 microprogramming 을 이용한 방식으로 구현

◦

특정 instruction과 State에 매칭되는 Control Signal을 ROM에 정의해놓고 쓴다.

•

Design

Lab5

•

pipeline CPU를 구현해보자

•

여러 명령어를 시행하는 만큼, immediate register들이 필요하다.

•

뿐만 아니라 data hazard 문제 해결을 위한 Forwarding Unit을 사용한다.

◦

Load의 경우 forwarding을 해도 1 cycle은 delay를 시켜야한다.

◦

버블을 삽입하자.

•

Control Hazard를 해결하기 위해 BTB 방식을 채용한다.

◦

이 BTB는 2-bit saturation을 기반으로 동작

•

디자인

Lab6

•

지금까지의 Lab은 Load나 Store 시 메모리에 직접 접근한다.

•

이에 우리는 Cache를 구현하여, 1차로 Cache에 접근하고 2차로 메모리에 접근해서 가져오도록 구현

.jpg&blockId=1b87074d-017e-8069-9667-d5678d39e51d)